So, our goal is to modify BIOS firmware the way it does not set bit 4 of the HOSTC register.

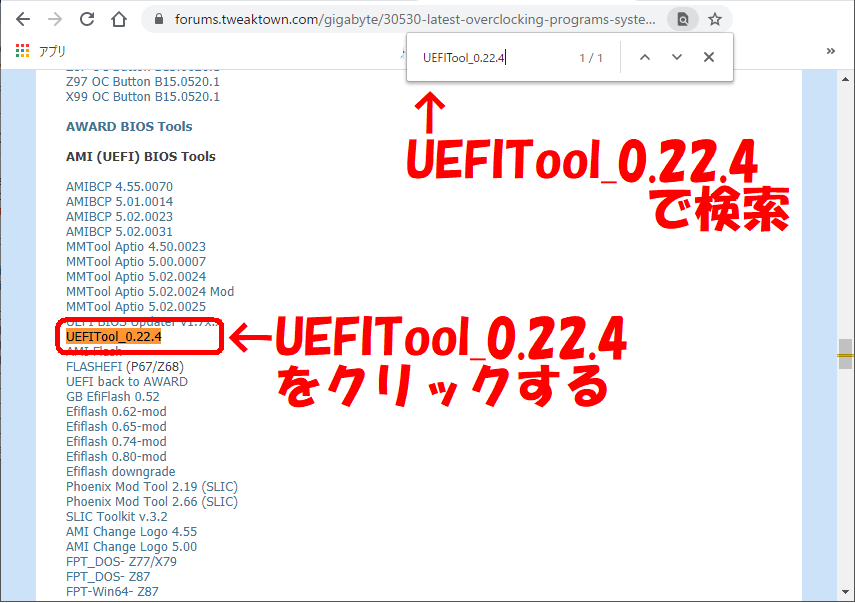

Unfortunately, our investigations confirmed that the bit is set by BIOS again once the hard reset has been initiated. #Uefitool gigabyte softwareThe PCH asserts PLTRST# during power-up and when software initiates a hard reset sequence through the Reset Control register (I/O port CF9h). The PCH asserts this signal to reset devices on the platform (such as SIO, FWH, LAN, processor, and so on). This bit can be cleared by on PLTRST# assertion only. ASUS, MSI, Biostar and other motherboard manufacturers meet this requirement, although ASRock, for example, does not protect SPD from programming within BIOS firmware. According to the bit description it should be set to “1”. #Uefitool gigabyte seriesSo, if we open the Intel 8 Series PCH datasheet (public edition) on page 667 we will find that the Host Configuration Register (HOSTC) of the SMBus Controller uses bit 4 called “SPD Write Disable” that was previously reserved. The only working solution is to modify BIOS. #Uefitool gigabyte windowsUnfortunately, software can’t temporarily bypass this restriction in Windows session. In some cases it was the only way to increase the memory bandwidth on notebooks. This means Intel does not want SPD to be programmed any more. The “SPD Write Disable” feature is implemented within Intel 9 Series Chipset Family PCH and X99 Chipset PCH as well. Now writes to SMBus addresses 50h - 57h are disabled by default via SMBus Host Controller registers. With release of 8 Series/C220 Series Chipset Family Platform Controller Hub (PCH) Intel introduce a great surprise for all of us. #Uefitool gigabyte how to

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed